Use Vivado to build an Embedded System

Objectives

After completing this lab, you will be able to:

- Create a Vivado project for a Zynq system.

- Use the IP Integrator to create a hardware system.

- Use Vitis IDE to create a standard memory test project.

- Run the test application on the board and hence verify hardware functionality.

Steps

Create a Vivado Project

- Open Vivado by selecting Start > All Programs > Xilinx Design Tools > Vivado 2021.2

- Click Create Project to start the wizard. You will see the Create a New Vivado Project dialog box. Click Next.

- Click the Browse button of the Project Location field of the New Project and browse to {labs}, and click Select.

- Enter lab1 in the Project Name field. Make sure that the Create Project Subdirectory box is checked. Click Next.

- In the Project Type form select RTL Project, and check the box Do not specify sources at this time. Click Next

-

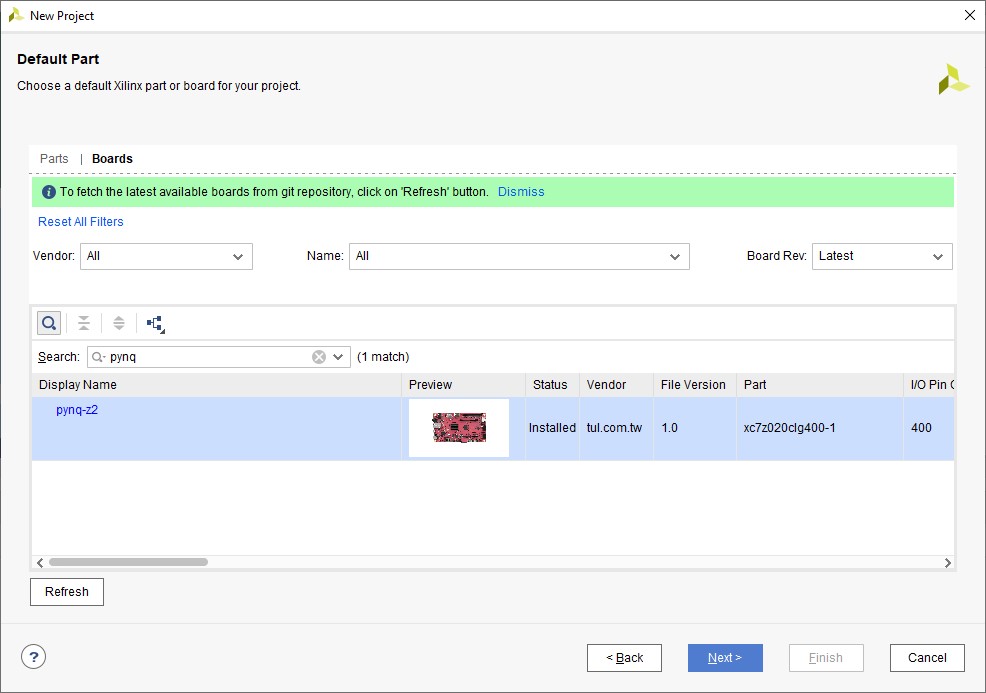

In the Default Part window, select the Boards tab, and depending on the board you are using, (if you can’t find the board you are looking for, refer to

for setup) and click Next.

Boards and Parts Selection

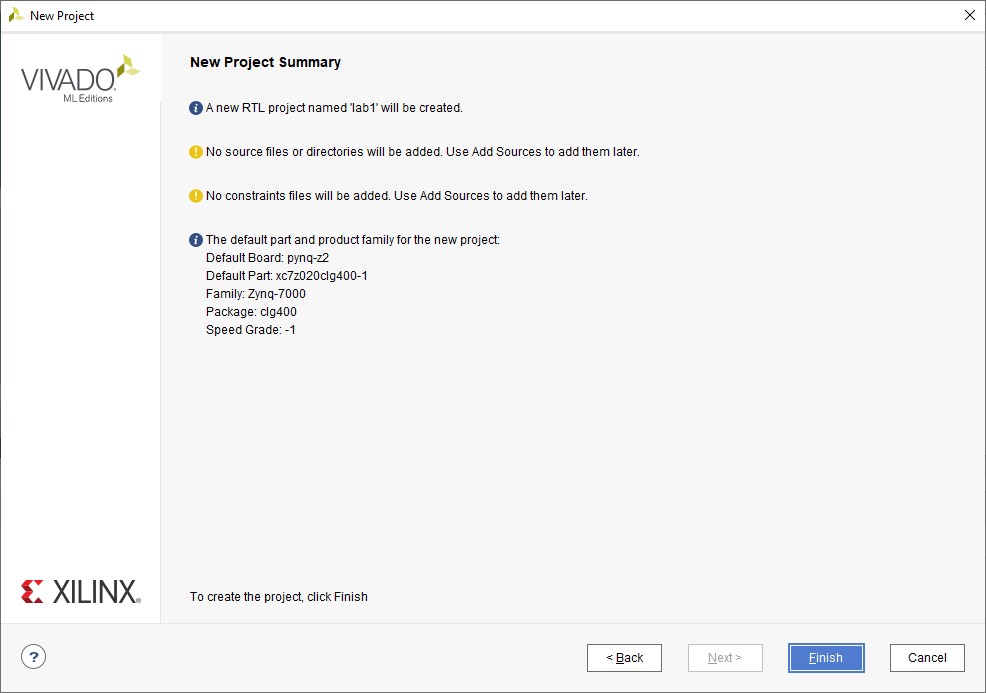

- Check the Project Summary (should be similar to what you see below) and click Finish to create an empty Vivado project.

Project Summary

Creating the System Using the IP Integrator

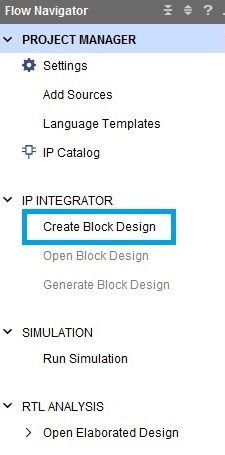

- In the Flow Navigator, click Create Block Design under IP Integrator.

Create IP Integrator Block Diagram

-

Enter system for the design name and click OK.

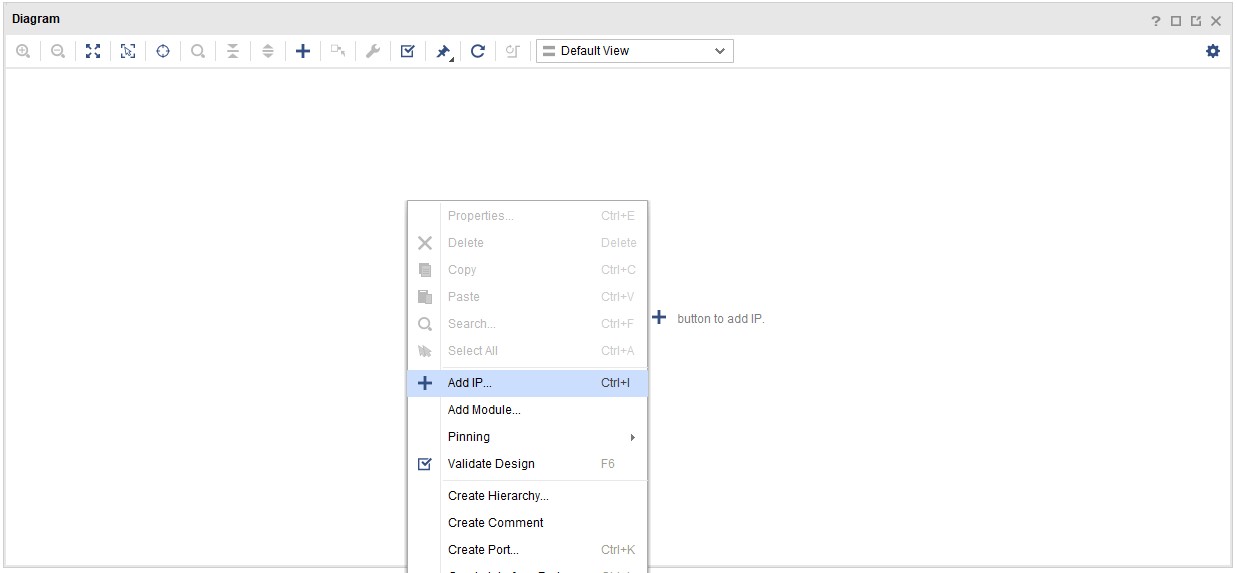

- Right-click anywhere in the Diagram workspace and select Add IP.

Add IP to Block Diagram

-

Once the IP Catalog opens, type “zynq” into the Search bar, find and double click on ZYNQ7 Processing System entry, or click on the entry and hit the Enter key to add it to the design.

-

Notice the message at the top of the Diagram window in a green label saying that Designer Assistance available. Click Run Block Automation.

-

A new window pops up called the Run Block Automation window. In it, select /processing_system7_0, leave the default settings and click OK.

-

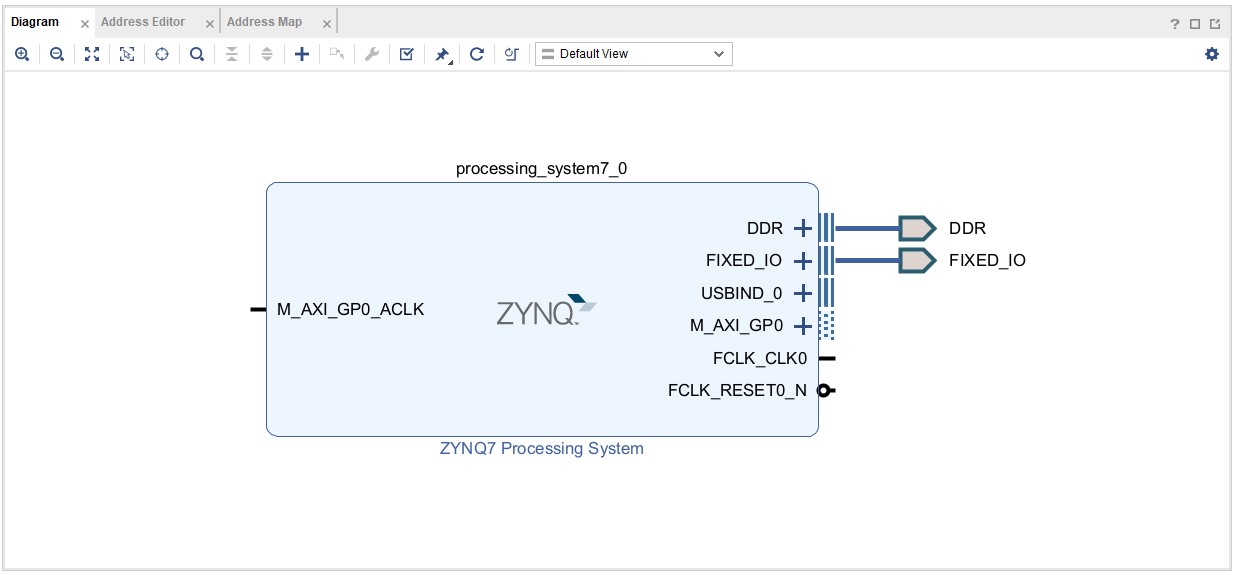

Once Block Automation has been completed, notice that ports have been automatically added for the DDR (double data rate, a type of memory) and Fixed IO, and some additional ports are now visible. The imported configuration for the Zynq related to the board has been applied which will now be modified. The block should finally look like this:

Zynq Block with DDR and Fixed IO ports

- Double-click on the added block to open the Customization window. Notice now the Customization window shows selected peripherals (with tick marks). This is the default configuration for the board applied by the block automation.

Configure the processing block with just UART 1 peripheral enabled.

-

A block diagram of the Zynq should now be open again, showing various configurable blocks of the Processing System.

-

At this stage, the designer can click on various configurable blocks (highlighted in green) and change the system configuration.

-

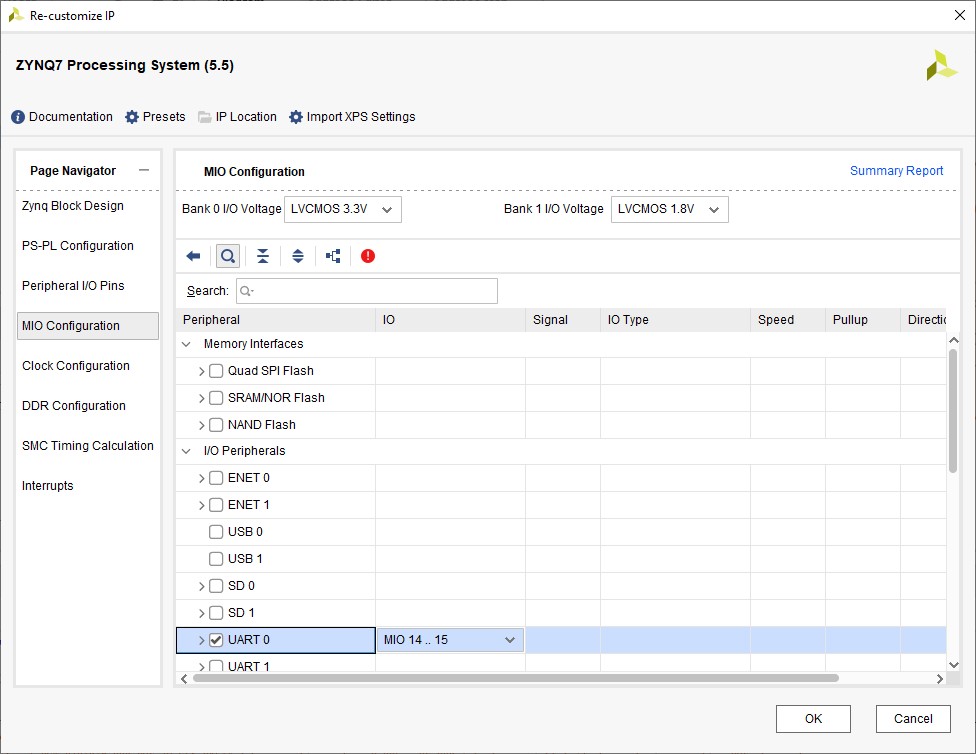

Click on one of the peripherals (in green) in the Peripheral I/O Pins block of the Zynq Block Design, or select the MIO Configuration tab on the left to open the configuration form

-

Expand Peripheral I/O Pins if necessary, and ensure all the following I/O peripherals are deselected except UART 1.

Note : Select UART 0 for PYNQ-Z2 instead of UART 1

i.e. Remove: ENET

USB 0

SD 0

Expand GPIO to deselect GPIO MIO

Expand Memory Interfaces to deselect Quad SPI Flash

Expand Application Processor Unit to disable Timer 0. </i>

Selecting only UART 1

-

Select the PS-PL Configuration tab on the left.

-

Expand AXI Non Secure Enablement > GP Master AXI interface and deselect M AXI GP0 interface.

-

Expand General > Enable Clock Resets and deselect the FCLK_RESET0_N option.

-

Select the Clock Configuration tab on the left. Expand the PL Fabric Clocks and deselect the FCLK_CLK0 option and click OK.

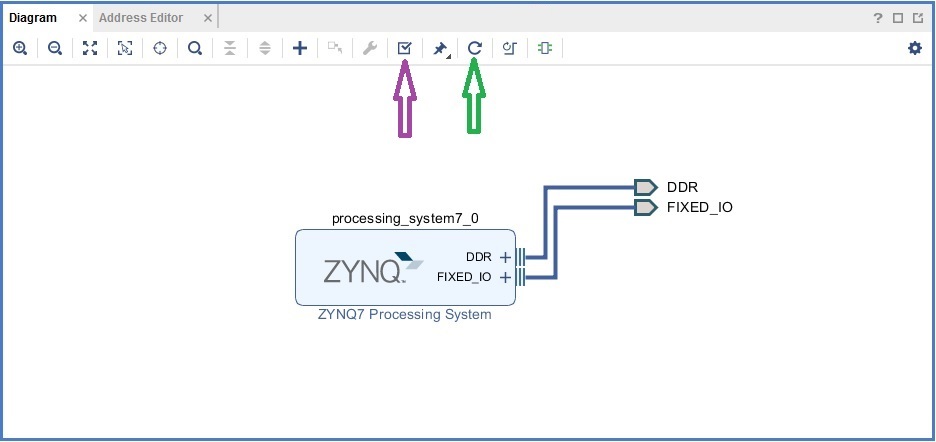

- Click on the Regenerate Layout button (green arrow) shown below:

Regenerating and Validating Design

- Click on the Validate Design button (purple arrow) and make sure that there are no errors.

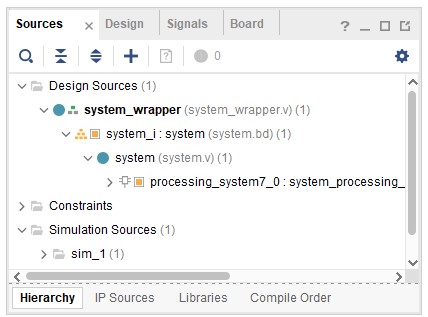

Generate Top-Level and Export hardware

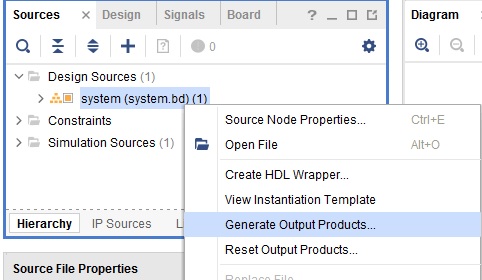

- In the sources panel, right-click on system.bd, and select Generate Output Products… and click Generate to generate the Implementation, Simulation and Synthesis files for the design (You can also click on Generate Block Design in the Flow Navigator pane to do the same).

Generating output products

-

Right-click again on system.bd, and select Create HDL Wrapper… to generate the top-level VHDL model. Leave the Let Vivado manager wrapper and auto-update option selected, and click OK.

The system_wrapper.v file will be created and added to the project. Double-click on the file to see the content in the Auxiliary pane.

The HDL Wrapper file generated and added to the project

- Notice that the Verilog file is already set as the top module in the design, indicated by the icon.

-

Select File > Export > Export hardware and click OK. (Save the project if prompted) Note: Since we do not have any hardware in Programmable Logic (PL) there is no bitstream to generate, hence the Include bitstream option is not necessary at this time.

- Basic information about the hardware configuration of the project can be found in the Xilinx Support Archive (XSA) file, along with the Address maps for the PS systems, and driver information. The .xsa file is used in the software environment to determine the peripherals available in the system, and their location in the address map.

Generate Memory Test Application in Vitis IDE

- Select Tools > Launch Vitis IDE, and Select the workspace location with any given location path. Click Launch. The Vitis IDE opens.

- Review the Welcome page and close it. Click Create Application Project, and click Next.

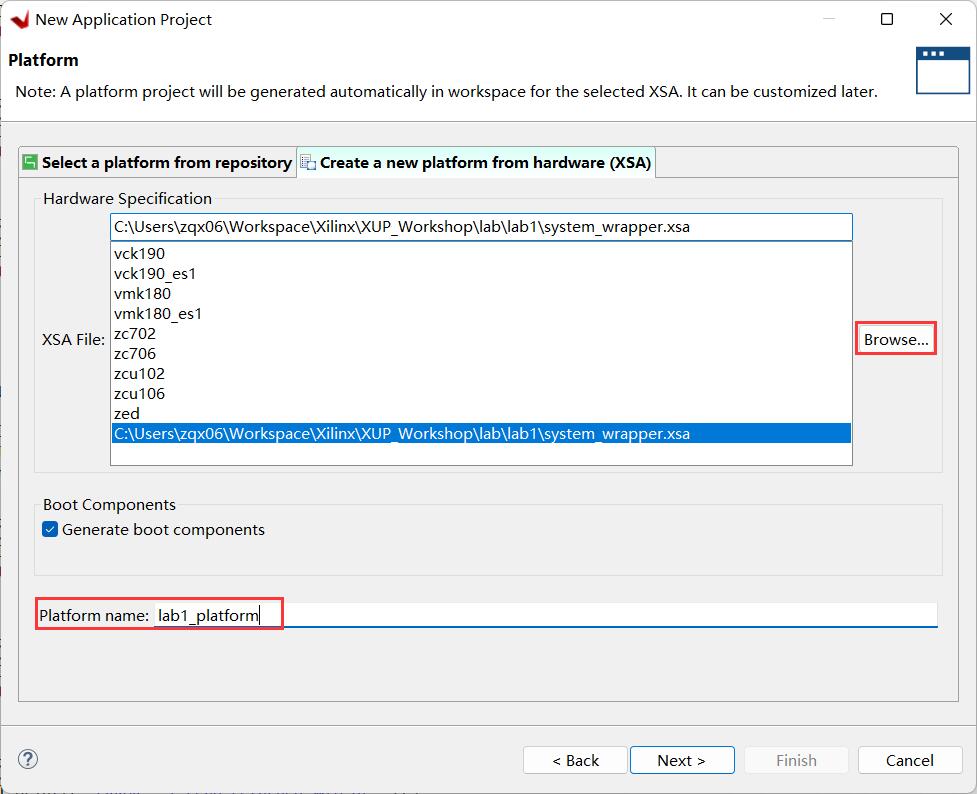

- In the Platform Selection window, select Create a new platform from hardware (XSA) and browse to select the system_wrapper.xsa file exported before. (Default is in the {labs}\lab1 folder).

- Enter lab1platform** as the _Platform name, click **Next.

Select a platform to create the project

-

In the project details window, name the project lab1, and in the Target Processor selection, select ps7_cortexa9_0.

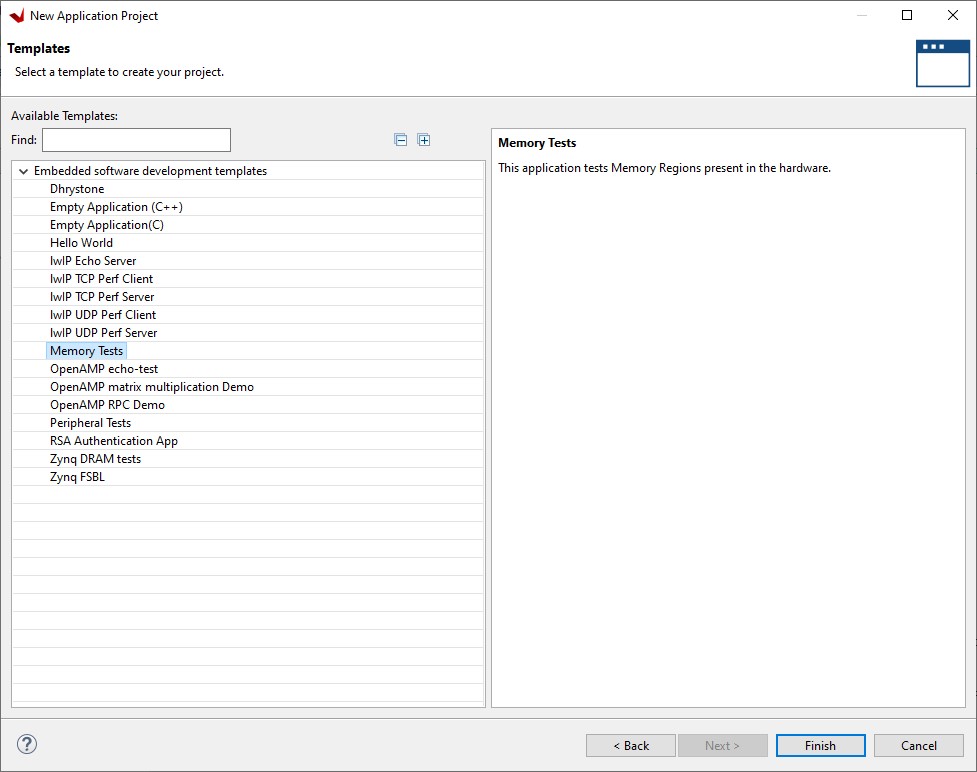

- Select Memory Tests as the template in the Template Selection window. Click Finish.

Select a template to create the project

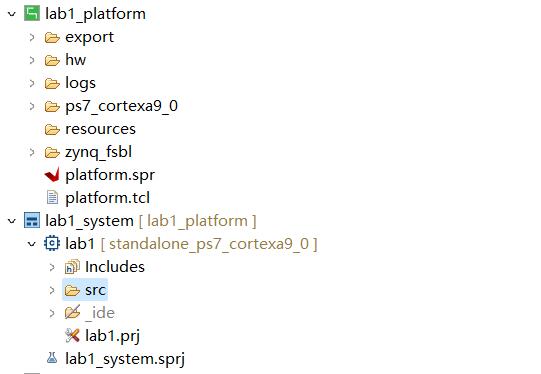

- Expand folders in the Explorer view on the left, and observe that there are two projects – lab1_platform, and lab1_system. The lab1_system project is the application that we will use to verify the functionality of the design. The lab1_platfrom is a platform project includes the ps7_init function which initializes the PS as part of the first stage bootloader. The Explorer view should look something like this:

The Project Explorer view

-

Open the memorytest.c file in the lab1_system > lab1 > src, and examine the contents. This file calls the functions to test the memory.

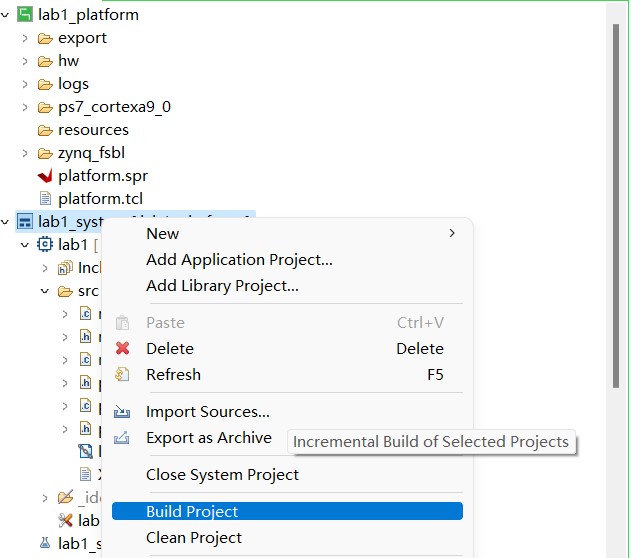

- Build the application project either by clicking the hammer button or by right-clicking on the application project and selecting Build Project as shown in following figure. As the project builds, you can see the output in the Console window.

Build the application project

Test in Hardware

- Make sure that micro-USB cable(s) is(are) connected between the board and the PC. Change the boot mode to JTAG. Turn ON the power of the board.

- Open a serial communication utility for the COM port assigned on your system. The Vitis software platform provides a serial terminal utility will be used throughout the tutorial. You can also use your preferred serial terminal application.

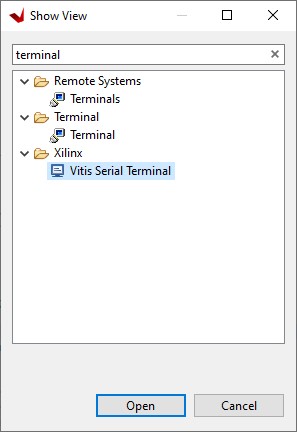

- To open this utility, select Window > Show view.

- In the Show View dialog box, type terminal in the search box.

- Select Vitis Serial Terminal and click Open.

Open the Vitis Serial Terminal

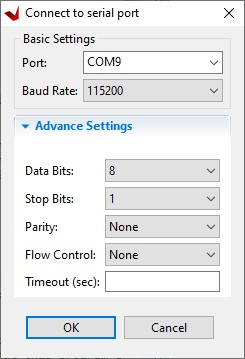

- Click the Add button in the Vitis Serial Terminal to connect to a serial terminal. Select the port from the dropdown menu. Keep the Advanced Settings as-is. Click OK.

Connect to serial port

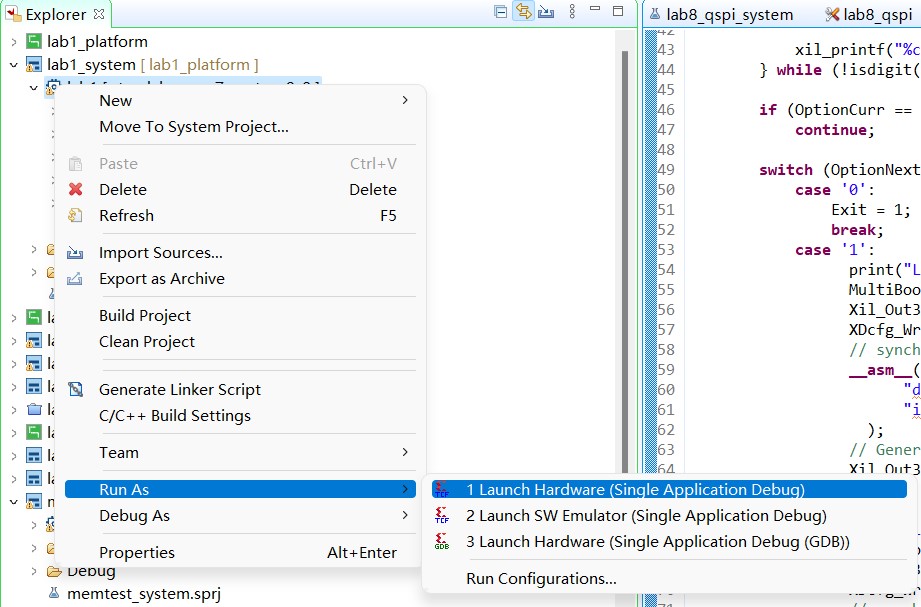

- Right-click lab1_system > lab1 and select Launch Hardware (Single Application Debug).

Launch Run Configurations

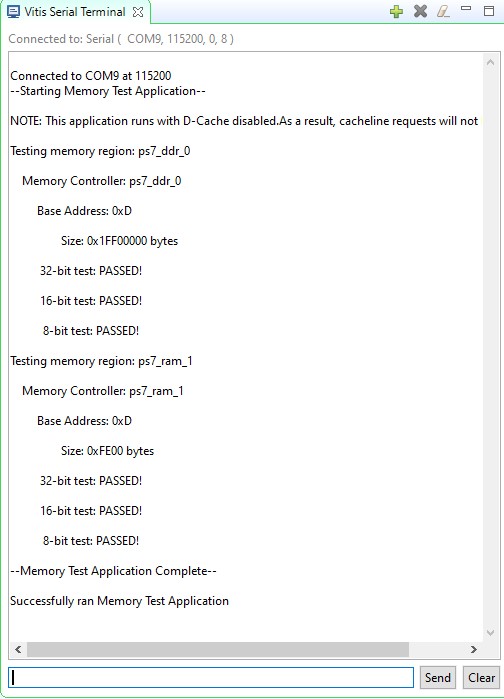

- You should see the following output on the Terminal tab.

Connect to serial port

- Close Vivado and Vitis IDE by selecting File > Exit in each program.

Conclusion

Vivado and the IP Integrator allow base embedded processor systems and applications to be generated very quickly. After the system has been defined, the hardware can be exported and Vitis IDE can be invoked from Vivado.

Software development is done in Vitis IDE which provides several application templates including memory tests. You verified the operation of the hardware by using a test application, executing on the processor, and observing the output in the serial terminal window.